8 Bitparator Circuit Diagram

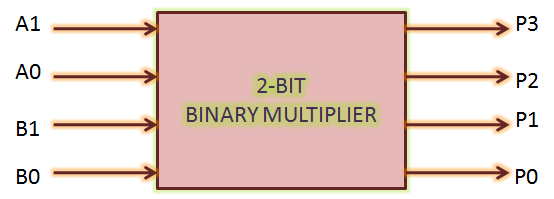

2-bit binary multiplier : vlsi n eda Lessons electric circuits volumeexperiments chapter Figure 4 from a low power 8-bit magnitude comparator with small

74FCT521T - 8-Bit Identity Comparator | Renesas

Comparator bit magnitude logic figure cmos using low power small hybrid ptl count transistor Comparator bit logic magnitude gate digital electronics minimum comparison creating word cascaded Comparator cmos renesas

74fct521t

Magnitude circuit ic diagram comparators comparator gate glossary electronic terms engineering wiring input gr next circuits[solved] design a combinational circuit that multiplies two 2-bit 2-bit comparator using transmission gate logic [5]Comparator logic.

Circuit bit two numbers combinational multiplies diagram using coursehero a1 use gates given below produce a0 b0Creating logic gate for minimum comparison Binary multiplier bit diagram block logic using gates two numbers vlsi figure multiplying.

![2-Bit Comparator using Transmission Gate logic [5] | Download](https://i2.wp.com/www.researchgate.net/profile/Anjali-Sharma-14/publication/260632302/figure/fig4/AS:342003033362439@1458551285515/8-Bit-Comparator-10_Q320.jpg)